**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

**Research Paper**

# Design and comparative analysis of inexact speculative adder and multiplier

K. Hari Kishore, B. K. V. Prasad, Y. Manoj Sai Teja\*, D. Akhila, K. Nikhil Sai, P. Sravan Kumar

VLSI Research Group, Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, Andhra Pradesh, India 522502 \*Corresponding Author Email: manojsaiteja@gmail.com

#### Abstract

A Carry look ahead adder is a sort of the summer used in the logic design of the digital systems. The CLA boost up the speed by decreasing the measure of duration needed to calculate the carry bits. The CLA based outline of the inexact speculative adder is pipelined architecture to incorporate couple of logic paths along its basic way and in this manner, improving the recurrence of operation. This paper presents the comparative analysis of the pipelined inexact speculative adder and the general carry look ahead adder and showed that the delay is reduced to 48.27% when compared to carry look ahead adder and also we have designed the pipelined multiplier using the Inexact speculative adders and observed that the delay is reduced to 48.32% when compared to the normal multiplier. This entail Xilinx ISE Design Suite 14.5 Tool.

Keywords: Inexact Speculative Adder, Multiplier, Carry Look Ahead Adder, Pipelining, Delay.

## 1. Introduction

The inexact speculative adder is designed in such a way that the carry propagation chain is splitted into multiple paths which are concurrently executed. Each path again contains a error compensation block, sub-adder block and a carry speculator block. The partial signal is generated by the speculator block and to give the local sum the sub adder block uses carry in. Faulty sums are corrected by the compensation block which corrects either local sum or reduces the magnitude in the error. The carry for speculation block is generated by using the bits in carry look ahead sourced either by dynamic or static input. Errors are distributed evenly by the latter in ETBA. Speculation faults are detected by the COMP block by comparing carry out and generated carry from the speculation block. The COMP block is implemented between ADD blocks. The addition is implemented by following five steps mainly. First for each sub-adder block , a carry-in is speculated from short carry propagation chain and next based on that carry in local sum is calculated by the sub adder. Faulty speculation is detected by comparing the carry in and the carry out of the sub adder. Correction of local sum is done when there is wrong speculation. Error magnitude is minimized by the balance of preceding sum bits if the correction is not possible. The inconsistency between expected carry and speculated carry is detected by the COMP block by using the XOR gate because of which error flag is created that triggers activation either error reduction or correction compensation techniques. The three main advantages of this technique is that optimization of block size, speculation and correction trade-off and error minimization and failed correction [1].

In the speculative addition with the variable latency CSPA block has carry and adder circuits. Carry predictor helps in prediction of carry out bit. And adder has three internal components namely multiplexer which consists of multi bit, the sum generator and also an internal carry generator. Carry out bit of the adder block is predicted by the carry predictor. Internal signals to be used in the sum generator are produced by the internal carry signals. Multiplexer takes the input from the carry predictor and selects on of the carry signals. Sum generator calculates the partial sum bits of adder block. The proposed method works as follows, internal carry generators and predictors work simultaneously when input patterns arrive. The carry out bit of the predictor is given to next block adder and it is the selector for multiplexer and next internal carry signal is determined and is sent to the sum generator. Error recovery and detection circuit is also used. Error signal is 0 when there is no error and valid signal becomes 1 when an error occurs error and valid signal becomes vice versa during error input registers becomes disable and no input is taken [2].

The carry speculative adder with modification of carry generators that uses only less number of gates. In order to get data continuously into circuit the data latching circuit is used. To get results accurately the error recovery and detection circuit is included. The CSPA is implemented in a way that in the modified adder block sum and carry generators are separated by an logic which results in increase of area and consumption of power. To minimize the area two carry generators are for carry in=1 and carry in=0 used instead of one. AND gate is replaced in the place of 1bit carry generator for carry in=1 and carry in=0 it is replaced with OR gate. Two types of modified carry generators are used in place of two carry generators which has one gate delay with very less area.

These generators produce carry without using Cin bit. In the design of variable latency CSPA the circuits such as error recovery, error detection, data latching are used [3]. When the input is received the output sum is given by the circuit (VLCSPA). Error block signals and error signals is given by the error detection circuit. Multiplexer which is multibit takes the input from the recovery circuit and cspa when it is 1 signal recovery is from recovery circuit and when it is 0 result is selected from CSPA. Input registers become disabled when an error occurs and no input is taken and XOR gate is used in place of not gate and ex-or operation is used between error signal and its compliment.

#### 2. Proposed Inexact Speculative Adder

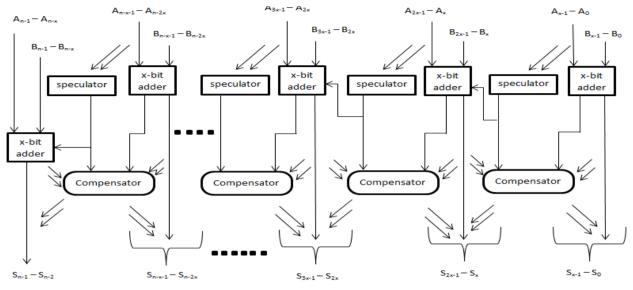

There are many drawbacks in adders such as high area, high path delay and very high power consumption. To overcome all these problems speculative adders are implemented which has both techniques of speculation and correction that helps in achieving low power, high speed and area efficient design when compares with the existing adders. The inexact speculative adder consists of blocks they are adder, speculator and compensator as shown in the Fig.1 [4].

Fig. 1: General Block diagram of inexact speculative adder

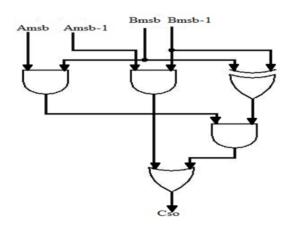

Fig. 2: Logic level representation of speculator

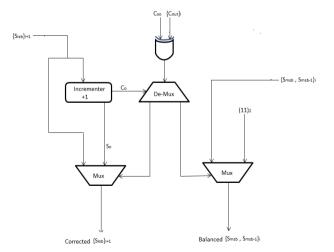

Fig. 3: Implementation of the compensator block

#### A. About Adder And Speculator

Two n- bit operands for the addition are represented by  $A=A_0,A_1,A_2,\ldots,A_{n-1}$  and  $B=B_0,B_1,B_2,\ldots,B_{n-1}$  and the carry in , carry out and sum is represented by  $C_{in}$ ,  $C_{out}$  and

$$\mathbf{S}_i = \mathbf{P}_i \bigoplus \mathbf{C}_i \tag{1}$$

The speculator block evaluates the carry based on the equations given below.

$$G_{i} = A_{i} \cdot B_{i} \tag{2}$$

$$P_i = A_i \bigoplus B_i \tag{3}$$

$$C_{i+1} = P_i \cdot C_i + G_i \tag{4}$$

Where  $P_i$  represents the carry propagate and  $G_i$  represents the carry generate.

#### **B.** About Compensator

This block compares the output carry from each adder block with the corresponding speculated carry using the xor gate. If the output of xor gate is zero then the sum is directly passed through the final output. Identically, if the xor gate output is one then it specify that error has been occurred which may be either positive or negative. The positive error specify the speculation of zero instead of one had occurred and indicates too low sum. The negative error specifies the speculation of one instead of zero had occurred and indicates too high sum. The compensator block carry out the unsigned accretion and depletion to the cluster of LSBs in this way the too high error is solved by a -1 and too low by a +1. In case of the overflow, the compensator block equalizes a cluster of MSBs of the predating adder in the opposite direction of the error as shown in the Fig 3 [1][4].

#### 3. Design Methodology

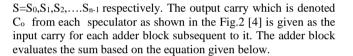

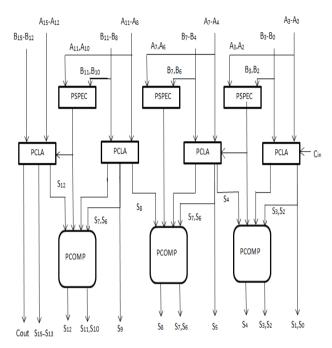

The pipelined architecture of inexact speculative adder reduces the delay and gives the high speed. So as shown in the Fig.4 [4] it comprises of three main blocks they are pipelined speculator, pipelined carry look ahead adder and the pipelined compensator

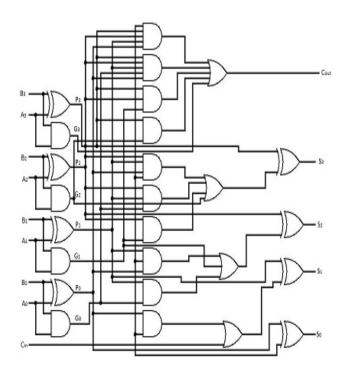

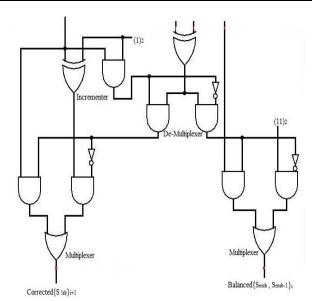

for 16 bit addition. Pipelined CLA of 4 bits is used here. For the first pipelined is given the carry in and for the succeeding ones the output carry from the pipelined speculator is given. It consists of five pipelined stages for the achievement of speed. The pipelined CLA is shown in the Fig. 5 has one pipelined stage with the inputs  $A_0$ - $A_4$  and  $B_0$ - $B_4$  and the C<sub>in</sub> and outputs are C<sub>out</sub> and S<sub>0</sub>-S<sub>4</sub> respectively. And now Coming to the pipelined compensator of pipelined stage comprises of the multiplexer, incrementor and the de-multiplexer as shown in the Fig.6 [1],[4].

Fig. 4: Pipelined inexact speculative adder

Fig. 5: Pipelined carry look ahead adder of four bits

Fig. 6: Logic level of the pipelined compensator

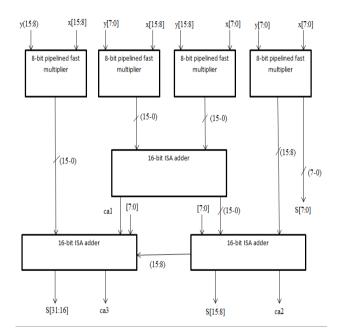

Fig. 7: Pipelined fast multiplier of 16-bit using ISA adders

As we know that the multiplication is fundamental building block of many digital designs there is need of having the multipliers that achieve the high speed and the low power. So one of the method is the use of The speculative multiplier can be done by using the methods such as carry-save tree and the carry speculation compression and by carry-save reduction tree have been explained in the literature [5]-[7]. Here we have designed the pipelined fast multiplier using the ISA adders of 16-bits using the 8-bit pipelined fast multiplier and 16-bit ISA adders. By using this method, we have achieved the high speed and reduced the delay.

#### 4. Simulation Results and Tables

The Fig.8 shows the output of the pipelined 16 bit inexact speculative adder based CLA for the given inputs A,B,C<sub>in</sub> and gives output S and C<sub>out</sub> respectively. Fig.9 shows the output of the normal 16-bit carry look ahead adder for the given inputs and the respective outputs are generated. Fig.10 shows the output of the pipelined fast multiplier of 16-bit using the ISA adder for given inputs A and B and output C is generated. Fig.11 shows the output of the conventional 16-bit multiplier for the given inputs and outputs are generated.

|             |             |                |        |        |                 |        |     | 518.333 ns |       |

|-------------|-------------|----------------|--------|--------|-----------------|--------|-----|------------|-------|

| Name        | Value       | 0 ns           | 100 ns | 200 ns | 300 ns          | 400 ns | 500 | ns         | 600 r |

| S[15:0]     | 10111101111 | 1110111011101  | <      |        | 10111101111011  | 1      |     |            |       |

| 16 солт     | 1           |                |        |        |                 |        |     |            |       |

| = 📷 A[15:0] | 10111110111 | 1110111011101  |        |        | 10111110111110  | 10     |     |            |       |

| B[15:0]     | 11111011100 | 0000000000000  |        |        | 111110111001010 | 01     |     |            |       |

|             | 0           |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             |                |        |        |                 |        |     |            |       |

|             |             | X1: 518.333 ns |        |        |                 |        |     |            |       |

#### Fig. 8: Pipelined 16-bit ISA based CLA output

|             |             |                  |            |                 |            |            | 1,000,000 ps |

|-------------|-------------|------------------|------------|-----------------|------------|------------|--------------|

| Name        | Value       | 999,995 ps       | 999,996 ps | 999,997 ps      | 999,998 ps | 999,999 ps | 1,000,000 ps |

| ► 👩 s[15:0] | 01101010010 |                  |            | 10101001011110  |            |            |              |

| 16 cout     | 1           |                  |            |                 |            |            |              |

| ▶ 📲 a[15:0] | 11100100101 |                  | 11         | 100100101011111 |            |            |              |

| ▶ 📲 b(15:0) | 10000101101 |                  | 10         | 00010110101111  |            |            |              |

| ୀର୍ଦ୍ଧ cin  | 0           |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             |                  |            |                 |            |            |              |

|             |             | X1: 1,000,000 ps |            |                 |            |            |              |

## Fig. 9: Normal 16-bit carry look ahead adder output

|             |             |                  |             |                  |            |            | 1,000,000 ps |

|-------------|-------------|------------------|-------------|------------------|------------|------------|--------------|

| Name        | Value       | 999,995 ps       | 1999,996 ps | 999,997 ps       | 999,998 ps | 999,999 ps | 1,000,000 ps |

| 🕨 🏹 c[31:0] | 00000000000 |                  | 000000000   | 0000000000001101 | 1000000    |            |              |

| 🕨 🏹 a[15:0] | 00000000001 |                  | 0           | 000000000100100  |            |            |              |

| ▶ 📷 b[15:0] | 0000000000  |                  | 0           | 000000000110000  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

|             |             | X1: 1,000,000 ps |             |                  |            |            |              |

|             |             |                  |             |                  |            |            |              |

Fig. 10: Pipelined fast multiplier 16-bit using ISA adders output

|             |             |                  |            |                  |            |            | 1,000,000 ps   |

|-------------|-------------|------------------|------------|------------------|------------|------------|----------------|

| Name        | Value       | 1999,995 ps      | 999,996 ps | 999,997 ps       | 999,998 ps | 999,999 ps | 1,000,000 ps 1 |

| ▶ 📲 c[31:0] | 0000000000  |                  |            | 0000000000011011 |            |            |                |

| ▶ 📷 a[15:0] | 00000000001 |                  | 00         | 00000000 100 100 |            |            |                |

| ▶ 📷 b[15:0] | 0000000000  |                  | 00         | 00000000110000   |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             |                  |            |                  |            |            |                |

|             |             | V1- 1 000 000    |            |                  |            |            |                |

|             |             | X1: 1,000,000 ps |            |                  |            |            |                |

Fig. 11: Conventional 16-bit multiplier output

Table.1: Comparison table for Normal carry look ahead adder with pipelined ISA adder

| Adder         | Logical delay(ns) | Routing delay (ns) | Total Delay (ns) |  |

|---------------|-------------------|--------------------|------------------|--|

| Normal        | 15.754            | 8.932              | 24.686           |  |

| Pipelined ISA | 8.749             | 4.020              | 12.769           |  |

Table.2:

Comparison table for Normal multiplier with pipelined ISA multiplier

| Multiplier    | Logical delay (ns) | Routing delay (ns) | Total Delay (ns) |  |

|---------------|--------------------|--------------------|------------------|--|

| Normal        | 57.722             | 39.354             | 91.076           |  |

| Pipelined ISA | 27.722             | 19.354             | 47.076           |  |

## 5. Conclusion

In this paper the detailed study and design and comparative analysis inexact speculative adders and multiplier was implemented for the reduced delay and high speed. From the above observations we can conclude that using of the inexact speculative adder based CLA improves the speed of execution over the normal carry look ahead adder and reduced the delay up to 48.27% and coming to the pipelined fast multiplier using the ISA adder improves the speed of execution when compared to normal multiplier and reduces the delay up to48.32%. We can also use the inexact speculative adders in many applications such as in multipliers, arithmetic and logic units and also used in the filters of the digital design.

### References

- Vincent Camus, Jeremy Schlachter, Christian Enz "Energy-Efficient Inexact Speculative Adder with High Performance and Accuracy Control" in Circuits and Systems (ISCAS) IEEE International Symposium on ,May 2015 pp.45-48.

- [2] Ing-Chao Lin, Yi-Ming Yang, Cheng-Chian Lin"high performance low power carry speculative adde with VARIABLE LATENCY" in IEEE Transactions on Very Large Scale Integration (VLSI) Systems Volume: 23, Issue: 9, Sept. 2015.

- [3] Y. PRUDHVIBHASKAR,S K AHEMED ALI, B V PAVAN KUMAR "PERFORMANCE IMPROVEMENT AND AREA OPTIMIZATION OF CARRY SPECULATIVE ADDITION

USING MODIFIED CARRY GENERATORS" in International Journal of Scientific Research Engineering & Technology (IJSRET) Volume 5, Issue 2, February 2016.

- [4] Rahul Shrestha "High-Speed and Low-Power VLSI-Architecture for Inexact Speculative Adder" in VLSI Design, Automation and Test (VLSI-DAT), 2017 International Symposium on April 2017.

- [5] Alessandro Cilardo, DavideDeCar, NicolaPetr, Francesco Caserta, Nicola Mazzocca, Ettore Napoli, Antonio Giuseppe Maria Strollo" High Speed Speculative Multipliers Based on Speculative Carry-Save Tree" in IEEE Transactions on Circuits and Systems I: Regular Papers Volume: 61, Issue: 12, Dec. 2014

- [6] Anju Sunny, Binu K. Mathew" Design of High Speed Approximate Multiplier with Carry Speculation Compressor" in IJSTE - International Journal of Science Technology & Engineering, Volume 2, Issue 4, October 2015.

- [7] Alfiya V M, Meera Thampy" High Speed Speculative Multiplier Using 3 Step Speculative Carry Save Reduction Tree" in IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) p- ISSN: 2278-8735. PP 65-72.

- [8] Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks & Soft Computing, ISSN:978-1-4799-3486-7/14, pp.270-273, August 2014.

- [9] Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- [10] P Bala Gopal, K Hari Kishore, R.R Kalyan Venkatesh, P Harinath Mandalapu "An FPGA Implementation of On Chip UART Testing with BIST Techniques", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34047-34051, August 2015

- [11] A Murali, K Hari Kishore, D Venkat Reddy "Integrating FPGAs with Trigger Circuitry Core System Insertions for Observability in Debugging Process" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.11, Issue No.12, page: 2643-2650, December 2016.

- [12] Mahesh Mudavath, K Hari Kishore, D Venkat Reddy "Design of CMOS RF Front-End of Low Noise Amplifier for LTE System Applications Integrating FPGAs" Asian Journal of Information Technology, ISSN No: 1682-3915, Vol No.15, Issue No.20, page: 4040-4047, December 2016.

- [13] N Bala Dastagiri, Kakarla Hari Kishore "Reduction of Kickback Noise in Latched Comparators for Cardiac IMDs" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.43, Page: 1-6, November 2016.

- [14] S Nazeer Hussain, K Hari Kishore "Computational Optimization of Placement and Routing using Genetic Algorithm" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.47, page: 1-4, December 2016.

- [15] Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and

Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- [16] N Bala Dastagiri,, K Hari Kishore "Analysis of Low Power Low Kickback Noise in Dynamic Comparators in Pacemakers" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.44, page: 1-4, November 2016.

- [17] P Ramakrishna, K. Hari Kishore, "Design of Low Power 10GS/s 6-Bit DAC using CMOS Technology "International Journal of Engineering and Technology, ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 226-229, January 2018.

- [18] A Murali, K. Hari Kishore, "Efficient and High Speed Key Independent AES Based Authenticated Encryption Architecture using FPGAs "International Journal of Engineering and Technology, ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 230-233, January 2018.

- [19] Y Avinash, K Hari Kishore 'Designing Asynchronous FIFO for Low Power DFT Implementation'' International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 8, Page No: 561-566, September 2017.

- [20] G.S.Spandana, K Hari Kishore "A Contemporary Approach For Fault Diagnosis In Testable Reversible Circuits By Employing The Cnt Gate Library" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 537-542, September 2017.

- [21] K.Hari Kishore, P. Sri Vidhya, A. Bhavana, O. Venkata Krishna "Comparison of Power Dissipation of ALU by using Different Technologies" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 399-403, September 2017.

- [22] Avinash Yadlapati, Dr. Hari Kishore Kakarla, "An Advanced AXI Protocol Verification using Verilog HDL", Wulfenia Journal, ISSN: 1561-882X, Volume 22, No: 4, pp. 307-314, April2015.

- [23] T. Padmapriya and V. Saminadan, "Inter-cell Load Balancing technique for multi-class traffic in MIMO-LTE-A Networks", International Journal of Electrical, Electronics and Data Communication (IJEEDC), ISSN: 2320- 2084, vol.3, no.8, pp. 22-26, Aug 2015.

- [24] S.V.Manikanthan and K.Baskaran "Low Cost VLSI Design Implementation of Sorting Network for ACSFD in Wireless Sensor Network", CiiT International Journal of Programmable Device Circuits and Systems, Print: ISSN 0974 – 973X & Online: ISSN 0974 – 9624, Issue : November 2011, PDCS112011008.

- [25] R. Kalaivani, K. Ramash Kumar, S. Jeevananthan, "Implementation of VSBSMC plus PDIC for Fundamental Positive Output Super Lift-Luo Converter," Journal of Electrical Engineering, Vol. 16, Edition: 4, 2016, pp. 243-258.