**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# A Short Paper on Testability of a SoC

T. Anil Chowdary<sup>1</sup>, M Durga Prasad<sup>2</sup>

Department of ECE, Koneru Lakshmaiah Education Foundation, Vaddeswaram, Guntur, Andhra Pradesh, India \*Corresponding Author Email: <sup>1</sup>aniltummala@kluniversity.in

# Abstract

The latest advances in semiconductor mix improvement accomplished assembling of expansive number of areas on a solitary chip Test organizing is an essential issue in System on-a-chip (SOC) test mechanization. Effective test masterminds minimize the general structure test application time, keep away from test asset clashes, and most outrageous power scrambling amidst test mode. For solid system on-chip, the circuit ought to be without fault since a solitary blame is likely going to make the entire chip vain. Finding the obstructions and utilization of helpful measures for same chip would diminish the running cost of the structure. The remarkable move toward test cost emergency, where semiconductor test costs start to approach or beat in more expenses has driven test organizers to apply new reactions for the issue of testing System-On-Chip (SoC) masterminds containing different IP (Intellectual Property) centers. since it is not yet possible to apply non particular test structures to an IP focus inside a SoC, the progress of different close frameworks, and the landing of new industry measures, for instance, IEEE 1500 and IEEE 1450.6, may begin to change this condition. This paper looks rules and at several systems at present utilized by SoC tests engineers [14].

Keywords: System On-Chip, BIST, Test Access Mechanism, CUT.

# 1. Introduction

Testing is a noteworthy in the framework reconciliation [2], [3] which chooses the request in which the different cores are tried. To accomplish high fault coverage a blend of implicit individual test and outer testing must frequently be utilized. A viable testing approach must minimize testing time while tending to the accompanying issues: 1) asset clashes between centers emerging from the utilization of shared TAMs and on-chip BIST motors; 2) priority imperatives among tests; and 3) control scattering requirements

## 2. Literature Review

The faults can't be recognized by applying test vectors alone. Because of such irregular example safe faults the Built-in self test approach regularly experiences fault coverage issue. This can be effectively enhanced by embedding extra rationale into the CUT [7]. The test set size decreases by utilizing Test Point Insertion (TPI) choice [7][8] in 1999 and 2000. Worked in self test (BIST) strategy produces test designs and assesses test reactions inside the chip]. In [9] the primitive delay faults were utilized. Primitive delay fault (PDF) implies a way defer fault in which circuit without timing imperfection and all primitive postpone deficiencies are considered.

In 2002 work on disclosure of parametric faults in basic circuit from input/output estimations was done as discussed in [11]. Defects bound to resistor, capacitor and inductor are discussed. They have figured coefficients of trade ability to

recognize the parametric faults and watched that there is most remote point in perceiving minimal size parametric faults in direct, time invariant basic circuits. In 2002 a coordinated way to deal with a few test scheduling issues is introduced in [1] to decide ideal calendars for sensibly estimated SOCs with priority connections, i.e., plans that protect alluring orderings among tests. It is an effective heuristic calculation to apply and analyze tests for vast SOCs with priority limitations in polynomial time. A novel calculation that utilizations appropriation of tests to acquire effective times for analyzation for SOCs is additionally portrayed which lessened CPU time. Priority imperatives force a fractional request among the tests in a test suite. This can be persuaded by a few elements. For instance, since BIST is probably going to identify a greater number of imperfections than an outside test focused on just at irregular safe shortcomings, it might be attractive to apply BIST first to a core amid assembling test. Thus, it might be alluring to test and analyze recollections prior so they can be utilized later for framework test. Since bigger cores will probably have abandons (because of their bigger silicon region), it might likewise be more alluring to test them first. Moreover, practically speaking tests are regularly reordered in view of test outcomes got from a little quality affirmation test. This data can be exploited to reorder tests with the end goal that potential low-yield modules in the last high-volume production batch are tested first. Inserting such priority imperatives in the test timetable can assume a vital part in expanding the general productivity of a test suite.

Preemptive test scheduling offers low testing time and altogether bring down computational unpredictability than correct strategies, to the detriment of test application overhead. Preemptive tests can be ended for a timeframe and afterward restarted, like the blocked multithreading approach utilized as a part of multipipeline chip.

A main consideration rousing the utilization of test seizure is that preemptive test schedules can be gotten in polynomial time, along these lines significantly diminishing calculation time, particularly since the general (no preemptive) scheduling issue is NP-Complete [2].

SOCs in test mode can scatter up to double the measure of force they do in ordinary mode, since centers that don't ordinarily work in parallel might be tried simultaneously to minimize testing time [4]. Power constrained test booking is thusly basic keeping in mind the end goal to confine the measure of simultaneousness amid test application to guarantee that the greatest power rating of the SOC is not surpassed. A reasonable coordinated way to deal with test booking for SOCs, in this way, commands the consideration of priority, test acquisition, and power requirements in the test plan.

In the year 2004 Keating and Meyer have finished leading tackle  $\Delta$ IDDQ testing. The present usage of the circuit changes if blame is accessible in the circuit and by separating the assortment of current use, the defective circuit can be isolated from blame free one. Because of process variety the reference voltage and leakage current moves in this way instead of using through and through regard, differential current is used to check the CUT. The IDDQ is measured by suggestion by including the clock time required to drop the voltage at segregated center point to drop underneath reference voltage level. The accuracy can be upgraded by changing clock frequency [6].

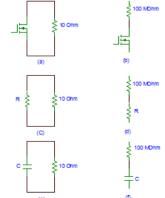

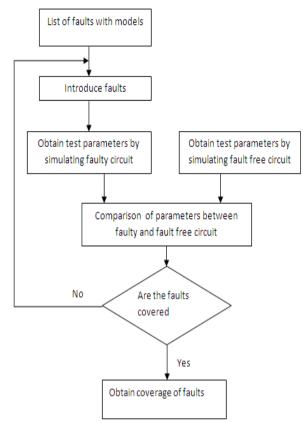

In the year 2007 Design-for-test strategies for opens in undetected branches in CMOS hooks and flip-flops have been proposed and talked about in [10]. In Integrated circuits with high thickness of contraptions different metal layers are required. These metal layers are associated by means of contacts. In such circuits there is chance of stuck open or resistive open blemishes which remain undetected in some branches. By including a little DFT equipment, it is possible to recognize both sorts of deficiencies in the CMOS snares and flip-flops without much execution degradation. In 2005 and 2007 the point the finger at models for MOSFET, resistor, capacitor are showed up in figure 1 and figure 2 exhibits stream chart on OBIST strategy for testing technique. The broken circuit is recognized from a deviation of its swaying parameters with respect to the faltering parameters under fault free conditions [12, 13] A couple of techniques have been proposed to crush the imperatives of set up STUMPS based method of reasoning BIST. These consolidate (i) deterministic BIST with periodic re-seeding either from the analyzer or through inward stockpiling [19], [20], (ii) on chip seed time segments [21], (iii) OPMISR (On-Product MISR) with just wellsprings of data being driven from ATE [22], (iv) Scan weight BIST with decompressors on chip [23], (v) X-tolerant BIST for X evade [24] and (vi) test-per clock sort circuitous BIST [25].

In 2014 distinct works related to testing and discovering issues in composed circuits is surveyed in [5]. The written work related to cutting edge and basic composed circuits fault is considered. In perspective of the written work for various accuse recognizing systems, the faltering based verifiable individual test (OBIST) procedure does not require shock generators or complex response analyzer and it is significant in testing straightforward and mixed banner consolidated circuits.

Fig. 1: Fault models (a) MOSFET stuck short (b) MOSFET stuck open (c) Resistor stuck short (d) Resistor Stuck open (e) Capacitor stuck short (f) Capacitor stuck open

Fig. 2: Flow chart on OBIST method for testing Procedure

## **3. SOC Test Architectures**.

### a) IEEE 1500

The IEEE 1500 standard was endorsed in late March 2005 after the IEEE P1500 SECT was begun ten years before in 1995. The extent of the standard characterizes a system for the trial of center outlines inside a SoC. This instrument constitutes equipment engineering and influences the CTL to encourage correspondence between center architects and center integrators [15]. The IEEE 1500 has two levels of consistence: a wrapped and unwrapped consistence. The wrapped consistence caters for a core that accompanies an IEEE 1500 wrapper work and a CTL program. The unwrapped consistence alludes to a center that does not have an (entire) IEEE 1500 wrapper but rather has a CTL portrayal. The IEEE 1500 is free of the usefulness of the IC or the inserted centers. The IEEE 1500 is another standard; however it has been generally expected and examined for various years, so this paper endeavors to take a gander at some other mechanical SoC test methods and endeavors to plot their levels of similarity with the IEEE 1500.

#### b) Philips TESTRAIL

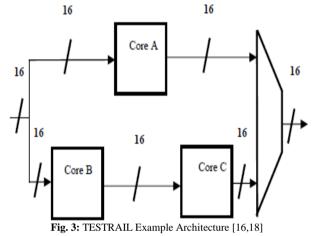

In the year 2000 the versatile TAM TESTRAIL made by Philips can offer access to no less than one core. A SoC contains more than one TESTRAIL each of fluctuating information exchange limit directed by the width of the TESTRAIL [16]. In the year 2000 the flexible TAM TESTRAIL made by Philips can offer access to no short of what one core interests. A SoC contains more than one TESTRAIL each of fluctuating data trade restrains coordinated by the width of the TESTRAIL [16]. The TESTRAIL approach endeavors to join both the attributes of TESTBUS and BST (Boundary Scan Test) [17]. BST is the IEEE 1149.1 standard for test find the opportunity to port and purpose of imprisonment take a gander at building. The TESTBUS building gifts the concentrations under test to be immediate gotten to from the pins of the IC. The TESTBUS approach can have no short of what one TESTBUS per SoC like TESTRAIL with the target that tradeoffs can be made between silicon range and test time [17]. Like BST, particular concentrations can be daisy-tied into one TESTRAIL. The TESTRAIL outlining is thusly a blend of daisy chain and dispersing models. A daisy chain building can be capable utilizing just a single TESTRAIL; while a portion design can be executed utilizing more than one TESTRAIL where each TESTRAIL shows independently [13]. A TESTRAIL case is appeared in figure 3. Core A has a private TESTRAIL of 16 bits, while the TESTRAILs both 16 bits of Core B and C is related. The two TESTRAILs from center An and from Core B and C are then multiplexed back onto one single 16-bit TESTRAIL. Figure 3 is an occurrence of the adaptability of TESTRAIL.

A daisy chain building can be proficient using only a solitary TESTRAIL, while an allotment configuration can be executed using more than one TESTRAIL where each TESTRAIL exhibitions self-sufficiently [13]. A TESTRAIL case is showed up in figure 3. Core A has a private TESTRAIL of 16 bits, while the TESTRAILs both 16 bits of Core B and C is associated. The two TESTRAILs from focus An and from Core B and C are then multiplexed back onto one single 16-bit TESTRAIL. Figure 3 is an instance of the flexibility of TESTRAIL.

#### 4. Proposed Work

Proposed work is to develop a Built-In Architecture which tests the cores of System On-Chip for Faults inside it in all respects like, Power supply noise, Stuck-at Faults, Stuck-open, Stuckshort, and all types of faults so that fault free reliable system is obtained as a result. Later on fault coverage of SoC will be improved to make a Design of SoC Testable to Possible extent.

#### References

- System-on-a-Chip Test Scheduling With Precedence Relationships, Preemption, and Power Constraints IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 21, no. 9, September 2002

- [2] K. Chakrabarty, "Test scheduling for core-based systems using mixedinteger linear programming," IEEE Trans. Computer-Aided Design, vol.19, pp. 1163–1174, Oct. 2000.

- [3] M. Sugihara, H. Date, and H. Yasuura, "A novel test methodology for core-based system LSIs and a testing time minimization problem," in Proc. Int. Test Conf., 1998, pp. 465–472.

- [4] V. Muresan et al., "A comparison of classical scheduling approaches in power-constrained block-test scheduling," in Proc. Int. Test Conf., 2000, pp. 882–891.

- [5] A Review of Methodologies for Testing and Locating Faults in Integrated Circuits. International Journal of Emerging Trends & Technology in Computer Science (IJETTCS) Volume 3, Issue 6, November-December 2014 ISSN 2278-6856

- [6] J. R. Vazquez and J. Pineda, "Built-in current sensor for Δlddq testing,"IEEE journal of solid state circuits, vol. 39, No. 3, March 2004.

- [7] M. J. Geuzebroek, J. Th. Vander Linden, and A. J. VandeGoor, "Test point insertion for compact test sets," ITC Int. Test Conf., pp. 292–300, 2000.

- [8] M. Yoshimura, T. Hosokawa, and M. Ohta, "A Test Point Insertion Method to Reduce the Number of Test Patterns," in Proc.11 the Asian Test Sym. (ATS'02), 2000.

- [9] A. Krstic, K. T. Cheng, and S. T. Chakradhar, "Primitive delay faults: Identification, testing, and design for testability," IEEE Tran. Comput.-Aided Design, vol.18, no. 6, pp 669–684, Jun 1999.

- [10] Z. Ramirez, G.Espinosa, and V.Champac, "Primitive delay faults: Identification, testing, and design for testability," IEEE Tran. VLSI Sys., vol. 15, no. 5, pp. 572–577, May 2007.

- [11] J. Savir, Z. Guo, "Test Limitations of Parametric Faults in Analog Circuits," Proc. of the 11th Asian Test Symposium. 2002.

- [12] S. R. Das, J. Zakizadeh, S. Biswas, M. H. Assaf, A. R. Nayak, E. M. Petriu, W. B. Jone, and M. Sahinoglu, "Testing Analog and Mixed-Signal Circuits With Built-In Hardware—A New Approach," IEEE Tran.on Instrum. Meas., vol. 56, no. 3, pp. 840–855, Jun. 2007.

- [13] S. R. Das, "Getting Errors to Catch Themselves-- Self-Testing of VLSI Circuits With Built-In Hardware," IEEE Tran. on Instrum. Meas., vol. 54, no. 3, pp. 941–955, Jun. 2005.

- [14] SoC Test: Trends And Recent Standards ITB Journal

- [15] IEEE, "IEEE Standard Testability Method for Embedded Corebased Integrated Circuits," in IEEE Std 1500-2005, 2005, pp. 0\_1-117.

- [16] K. Chakrabarty, "Design of system-on-a-chip test access architectures using integer linear programming," presented at VLSI Test Symposium, 2000. Proceedings. 18th IEEE, 2000.

- [17] Y. Zorian, E. J. Marinissen, and S. Dey, "Testing embedded-core based system chips," presented at Test Conference, 1998. Proceedings. International, 1998.

- [18] E. J. Marinissen, R. Arendsen, G. Bos, H. Dingemanse, M. Lousberg, and C. Wouters, "A structured and scalable mechanism for test access to embedded reusable cores," presented at Test Conference, 1998. Proceedings. International, 1998.

- [19] P.Wohl, J.Waicukauski, S.Patel and M.Amin, "Efficient Compression and Application of Deterministic Patterns in Logic BIST Architecture, Design Automation Conf., 2003, pp. 566-569.

- [20] P.Wohl, J.Waicukauski, S.Patel and M.Amin, "X-Tolerant Compression and Application of Scan ATPG Patterns in a BIST Architecture", Intl. Test Conf., 2003, pp. 727-736.

- [21] G.Kiefer, H.Vranken, E.J.Marinissen and H-J.Wunderlich, "Application of Deterministic Logic BIST on Industrial Circuits", JETTA, Vol. 17, Nos. 3/4, 2001, pp. 351-362.

- [22] C.Barnhart, V.Brunkhorst, F.Distler, O.Farnsworth, B.Keller and B.Koenemann, "OPMISR - The Foundation for Compressed ATPG Vectors", Intl. Test Conf., 2001, pp. 748-757.

- [23] J.Rajski, J.Tyszer, M.Kassab, N.Mukherjee, R.Thompson, K.H.Tsai, A.Hertwig, N.Tamarapalli, G.Mrugalski, G.Eide, J.Qian, "Embedded Deterministic Test for Low Cost Manufacturing Test", Intl. Test Conf., 2002, 301-310.

- [24] S.Mitra and K.S.Kim, "X-Compact: An Efficient Response Compaction Technique for Test Cost Reduction", Intl. Test Conf., 2002, pp. 311-320

- [25] C.Stroud, A Designer's Guide to Built-In Self-Test, Kluwer Academic Publishers, 2002.

- [26] Avinash Yadlapati, Dr. Hari Kishore Kakarla, "An Advanced AXI Protocol Verification using Verilog HDL", Wulfenia Journal, ISSN: 1561-882X, Volume 22, Number 4, pp. 307-314, April 2015

- [27] P Ramakrishna, K. Hari Kishore, "Design of Low Power 10GS/s 6-Bit DAC using CMOS Technology "International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 226-229, January 2018.

- [28] A Murali, K. Hari Kishore, "Efficient and High Speed Key Independent AES Based Authenticated Encryption Architecture using FPGAs "International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 230-233, January 2018.

- [29] G.S.Spandana, K Hari Kishore "A Contemporary Approach For Fault Diagnosis In Testable Reversible Circuits By Employing The CNT Gate Library" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 537-542, September 2017.

- [30] K Hari Kishore, CVRN Aswin Kumar, T Vijay Srinivas, GV Govardhan, Ch Naga Pavan Kumar, R Venkatesh "Design and

Analysis of High Efficient UART on Spartran-6 and Virtex-7 Devices", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 09, pp. 23043-23052, June 2015.

- [31] K Bindu Bhargavi, K Hari Kishore "Low Power BIST on Memory Interface Logic", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 08, pp. 21079-21090, May 2015.

- [32] Korraprolu Brahma Reddy, K Hari Kishore, "A Mixed Approach for Power Dissipation Reduction in Nanometer CMOS VLSI circuits", International Journal of Applied Engineering Research, ISSN 0973-4562 Volume 9, Number 18, pp. 5141-5148, July 2014.

- [33] Nidamanuri Sai Charan, Kakarla Hari Kishore "Reorganization of Delay Faults in Cluster Based FPGA Using BIST" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.28, page: 1-7, July 2016.

- [34] Sravya Kante, Hari Kishore Kakarla, Avinash Yadlapati,"Design and Verification of AMBA AHB-Lite protocol using Verilog HDL" International Journal of Engineering and Technology, E-ISSN No: 0975-4024, Vol No.8, Issue No.2, Page:734-741, May 2016.

- [35] Bandlamoodi Sravani, K Hari Kishore, "An FPGA Implementation of Phase Locked Loop (PLL)", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34137-34139, August 2015.

- [36] Avinash Yadlapati, Kakarla Hari Kishore, "Constrained Level Validation of Serial Peripheral Interface Protocol", Proceedings of the First International Conference on SCI 2016, Volume 1, Smart Computing and Informatics, Smart Innovation, Systems and Technologies 77, ISSN No: 2190-3018, ISBN: 978-981-10-5544-7, Chapter No: 77, pp. 743-753, 25<sup>th</sup> December 2017.

- [37] P Kiran Kumar, P Prasad Rao, Kakarla Hari Kishore, "Optimal Design of Reversible Parity Preserving New Full Adder / Full Subtractor", IEEE SPONSORED 3rd INTERNATIONAL CONFERENCE ON ELECTRONICS AND COMMUNICATION SYSTEMS (ICECS 2016), pp. 3465-3470, 25<sup>th</sup> and 26<sup>th</sup> February 2016.

- [38] Y Avinash, K Hari Kishore 'Designing Asynchronous FIFO for Low Power DFT Implementation' International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 8, Page No: 561-566, September 2017

- [39] Mahesh Mudavath and K Hari Kishore "Design of RF Front End CMOS Cascade CS Low Noise Amplifier on 65nm Technology Process" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 417-422, September 2017.

- [40] P. Sahithi K Hari Kishore, E Raghuveera, P. Gopi Krishna "DESIGN OF VOLTAGE LEVEL SHIFTER FOR POWER-EFFICIENT APPLICATIONS USING 45nm TECHNOLOGY" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 103-108, March 2018.

- [41] N Bala Dastagiri K Hari Kishore "A 14-bit 10kS/s Power Efficient 65nm SAR ADC for Cardiac Implantable Medical Devices" International Journal of Engineering and Technology (UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 34-39, March 2018.

- [42] K Hari Kishore, K Durga Koteswara Rao, G Manvith, K Biswanth, P Alekhya "Area, Power and Delay Efficient 2-bit Magnitude Comparator using Modified GDI Technique in Tanner 180nm Technology" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 222-226, March 2018.

- [43] Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- [44] P Bala Gopal, K Hari Kishore, R.R Kalyan Venkatesh, P Harinath Mandalapu "An FPGA Implementation of On Chip UART Testing with BIST Techniques", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34047-34051, August 2015