**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# An Efficient and Novel Design of Loop Filter, Charge Pump and VCO for PLL Using CMOS Technology

N AshokKumar<sup>1</sup>\*, A Kavitha<sup>2</sup>

<sup>1</sup>Associate Professor, Department of ECE, Sree Vidyanikethan Engineering College, Tirupati, India. <sup>2</sup>Professor, Department of ECE, Vel Tech Multi Tech Dr. Rangarajan Dr. Sakunthala Engineering College, Chennai, India. \*Corresponding author E-mail: drashokvlsi@gmail.com

#### Abstract

This article presents an occasional energy charge pump, low pass filter and voltage supervised generator for little energy section loop. PLL are generally used for synchronization and regulate of grid- associated power electronic techniques. The article enfolds the whole circuit figure of circle filter, charge pump and voltage restrict oscillator through 1.8v energy stock. This kind uses 0.18um CMOS technology. In recent times, voltage restricted oscillator are employed for phase lock loop. A great viable loop-bandwidth plan method, derivative from a distinct -time PLL additional complements the model, jitter attributes of а PLL previously somewhat evolved via optimizing precisecircuit elements. The expressed system no longer simplest guesstimates the timing jitter of a PLL, but additionally attains the most reliable bandwidth reducing the at the whole PLL jitter.

Keywords: Low Pass filter, charge pump, PLL, Phase frequency detector.

# 1. Introduction

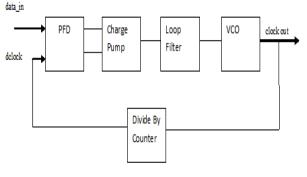

Digital PLL. is one amongst the normally predictable standards in cuttingedge day digital techn iques.PLL receives giantappliances to create and synchronize properly timed watches, renews signal from loud interface channel, FPGAs, interface techniques, frequency-synthesizer, trans-receivers. PLL are said to have preference, As a PLL having a solo chip [1]. Short energy DPLL is fetching primary for movable and battery initiated packed in electronics tool, thereby decreasing the threat of dependability troubles. The PLL does the multipurpose roles in timer production, synchronization and multiplication. Block diagram of PLL is shown in Fig 1. The proposed article is arranged as following, Part II includes charge pump, Part III discusses about low pass filter and Part VI describes about Voltage Limited Oscillator.

Fig. 1: Phase Locked Loop

# 2. Charge Pump

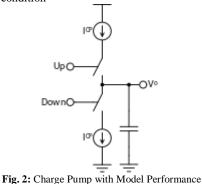

In Frequency Detector, Charge is one of the primary components. The production signs - RISE gesture and Down notices produced by Phase Frequency Detector are precisely related with the charge pump [3][5]. The block figure of perfect charge pump is exposed in figure.2. The output of pump is connect to a filter that combines the pump output current to an VCO control voltage (Vcntl)[7]. The pump fit to its filter output to below states:

State 1: Charging Condition: +ICP State2: Discharging Condition: -ICP State 3: Zero condition

Method of the charge pump possibly tabularized and it is the ultimate action of pump. It describes the controls of the charge pump. It charges or releases the present of the pump associated with rate of error sign (pulse width of the RISE or DOWN) created by the Phase Frequency Detector. The actions are listed in table.1.

| Table 1: Charge Fullip Operating Condition |        |             |                       |  |

|--------------------------------------------|--------|-------------|-----------------------|--|

| RISE                                       | DOWN   | Condition   | Note                  |  |

| Signal                                     | Signal |             |                       |  |

| 1                                          | 0      | Charging    | Icp flows into filter |  |

| 0                                          | 1      | Discharging | Icp flows out from    |  |

|                                            |        |             | filter                |  |

| 0                                          | 0      | Vout con-   | Icp=0                 |  |

|                                            |        | stant       |                       |  |

| 1                                          | 1      | Vout con-   | Icp=not 0             |  |

|                                            |        | stant       | _                     |  |

Table 1: Charge Pump Operating Condition

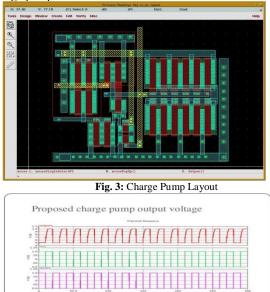

In Fig. 3 shows the CMOS Route based on Charge pump. The layout has been drawn employing Virtuoso. Fig. 4 is waveform of charge pump

Fig. 4: Transient Response

# 3. Loop Filter

ō

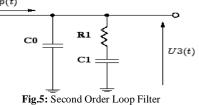

All Loop filter is important of PLL. It is conventional to decide filter rates correctly, as inappropriate ratios may lead the loop to oscillate for long without inward at the locked position or it can so occur that once locked little dissimilarities in the input data cancause the loop to unlock [1]. It is illustrated in Figure 5.  $I_{cp}(t)$

The consequent -order loop filter then the capacitor to stable of present points. This filter has two limits one at down frequency and other one is grand frequency and a neutral is add up the solidness [8]. The LPF is employed to put back the pump I to V. The output voltage of the loop filter observes the oscillation frequency of the VCO [6]. Filter output is augment if clock leads INFOR-MATION and diminish if INFORMATION leads the clock. If the PLL is maintains stable in the value of locked.

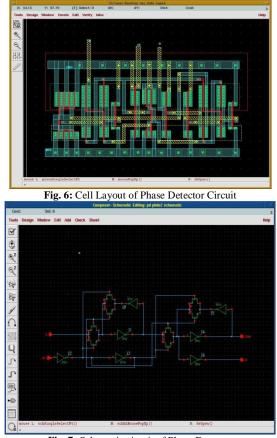

Fig. 7: Schematic circuit of Phase Detector

The cell layout of part detector is exposed in figure 6. The part detector circuit evaluates the output of the voltage restrict delay circuit with the suggestion clocking of the technique to charge or discharge the charge pump circuit [5]. The fundamental running theory is to utilize master-slave architecture to create the circuit vocation on the positive border [8]. Every set consists of two broadcast gates and two inverters, shaping a circuit with a stagnant latch. It can avert noise interference and vocation in extreme - velocity circuits. Therefore, this circuit can create the minor adjustments of the reference timer and voltage restricts delay line respond to the charge pump circuit. The whole part of the circuit is remunerated and exacted [9]. The architecture is exposed in figure 7.

# 4. Voltage Controlled Oscillator

VCO is a free framework and produces an occasional yield with no information flag. VCO is A oscillator outlined with the end goal that its wavering recurrence is controlled by a input voltage [3] [6]. The recent - starving VCO method is identical to the circle oscillator. The functionality of the plans are Vdd, Input Voltage, Technology, and Output Frequency having 1.8V, 90mv, 180nm and 1.53 GHz respectively.

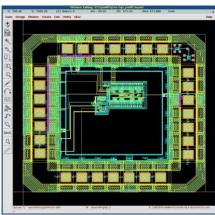

Fig. 9: Last Layout of the Design

## 5. Conclusion

In this paper, PLL ring method that hair the fraction of its output sign to the allusion signal. This is derived from the timer construction appliance. A PLL is accessible with enhance planning in CMOS equipment. The intention of this article is to reach above 1GHz and successfully accomplished 1.53GHz frequency. The oscillator produces returning sign, and the part detector communicates the part of that sign with the part of the input returning sign, modifying the oscillator to keep the parts organized Keeping the input and output phase in lock pace also gives keeping the input and output frequencies the alike. As a consequence, in adding to synchronizing signs, a phase-locked loop traces the input frequency, or it can stimulate a frequency that is several of the input frequency. These properties coordinate the PC timer, demodulation, and frequency fusion.

## References

- SrinivasGude; Chia-Chi Chu Dynamic Performance Improvement of Multiple Delayed Signal Cancellation Filters-based Three-Phase Enhanced-PLL, IEEE Transactions on Industry Applications 2018.

- [2] Omer CihanKivanc, SalihBarisOzturk, Sensor less PMSM Drive Based on Stator Feed forward Voltage Estimation Improved With MRAS Multi-Parameter Estimation, IEEE/ASME Transactions on Mechatronics 2018.

- [3] Precision Risk Analysis of Cancer Therapy with Interactive Nomo grams and Survival Plots. G. ElisabetaMarai; Chihua Ma; Andrew Burks; FilippoPellolio; Guadalupe M. Canahuate; David M. Vock; Abdallah SR Mohamed; Clifton David Fuller, IEEE Transactions on Visualization and Computer Graphics 2018

- [4] Adaptive Low-Pass Filter based DC offset Removal Technique for Three-Phase PLLs , ParagKanjiya; VinodMadhavraoKhadkikar; Mohamed ShawkyElMoursi IEEE Transactions on Industrial Electronics Year: 2018.

- [5] An Improved Feed forward Control Method Considering PLL Dynamics to Improve Weak Grid Stability of Grid-Connected InvertersXueguang Zhang; Xia Danni; Fu Zhichao; Gaolin Wang; DianguoXuIEEE Transactions on Industry Applications Year: 2018.

- [6] Study of Total-Ionizing-Dose Effects on a Single-Event-Hardened Phase-Locked Loop, Zhuojun Chen; Ding Ding; Yemin Dong; Yi Shan; Shuxing Zhou; Yuanyuan Hu; YunlongZheng; Chao Peng; Rongmei ChenIEEE Transactions on Nuclear Science Year: 2018.

- [7] A Synchro-Perspective-Based High-Frequency Voltage Injection Method for Position-Sensor less Vector Control of Doubly-Fed Induction Machines AnuwatSrivorakul; SurapongSuwankawin IEEE Transactions on Industry Applications Year: 2018.

- [8] Hybrid Phase Locked Loop for Controlling Master-Slave Configured Centralized Inverters in Large Solar Photovoltaic Power Plants Prashant Jain; VivekAgarwal; Bishnu Prasad MuniIEEE Transactions on Industry Applications Year: 2018.

- [9] A Ku-Band CMOS FMCW Radar Transceiver for Snowpack Remote SensingYanghyo Kim; Theodore J. Reck; Maria Alonso-del Pino; Thomas H. Painter; Hans-Peter Marshall; Edward H. Bair; Jeff Dozier; GoutamChattopadhyay; Kuo-Nan Liou; Mau-

Chung Frank Chang; Adrian TangIEEE Transactions on Microwave Theory and Techniques Year: 2018.

- [10] A 3.9 m W Bluetooth Low-Energy Transmitter Using All-Digital PLL-Based Direct FSK Modulation in 55 nm CMOS SeongJin Oh; SungJin Kim; Imran Ali; Truong Thi Kim Nga; DongSoo Lee; YoungGunPu; Sang-Sun Yoo; Minjae Lee; KeumCheol Hwang; Youngoo Yang; Kang-Yoon Lee IEEE Transactions on Circuits and Systems I: Regular Papers Year: 2018

- [11] G. Ramprabu, S. Nagarajan, "Design and Analysis of Novel Modified Cross Layer Controller for WMSN", Indian Journal of Science and Technology, Vol 8(5), March 2015, pp.438-444.